用SSI協(xié)議是如何實現(xiàn)的

絕對值編碼器?

近年來,編碼器得到了廣泛的應(yīng)用,主要用于工業(yè)控制系統(tǒng),如電機速度測量、機床位置測量、起重機爬升距離測量等。與此同時,編碼器在市場上的規(guī)模越來越大,工業(yè)需求也在增長。在未來幾十年,編碼器行業(yè)將達到快速發(fā)展的階段,更多的編碼器制造商將參與這場革命的競爭。

編碼器是一種將數(shù)據(jù)轉(zhuǎn)換為信號形式的設(shè)備,可用于通信、傳輸和存儲。編碼器的原理是將這些物理位移轉(zhuǎn)換為已知的電信號。根據(jù)工作類型的不同,編碼器可分為兩類:增量編碼器和絕對編碼器。增量編碼器主要用于精度要求較低的儀器。絕對編碼器通常用于具有高精度要求的行業(yè),如設(shè)備制造和電子產(chǎn)品。由于絕對編碼器具有啟動速度快、數(shù)字編碼和位置獨特的特點,因此被廣泛應(yīng)用于各種工業(yè)系統(tǒng)。隨著儀器儀表的日益智能化,人們對低功耗、高質(zhì)量、小尺寸的旋轉(zhuǎn)編碼器提出了要求。他們希望在絕對編碼器領(lǐng)域有更多類型的輸出方法,以便越來越多的設(shè)備能夠?qū)崿F(xiàn)自動化。

在早期,絕對編碼器的輸出大多使用并行輸出方法。然而,隨著技術(shù)的進步,絕對編碼器的輸出方式越來越多樣化,如RS-485、PROFIBUS DP、CAN、DeviceNet等現(xiàn)場總線輸出方式,模擬信號轉(zhuǎn)換輸出方式和SSI協(xié)議同步串行輸出方式。這些輸出方法都有各自的優(yōu)點和缺點。并聯(lián)輸出適用于短距離傳輸,價格相對較低;現(xiàn)場總線電源通常適用于大型工業(yè)領(lǐng)域,但相對昂貴;然而,模擬信號轉(zhuǎn)換和輸出方法的使用目前相對有限。與這些輸出方法相比,SSI串行輸出方法具有抗干擾性強、布線少等優(yōu)點,在市場上得到了廣泛的應(yīng)用。

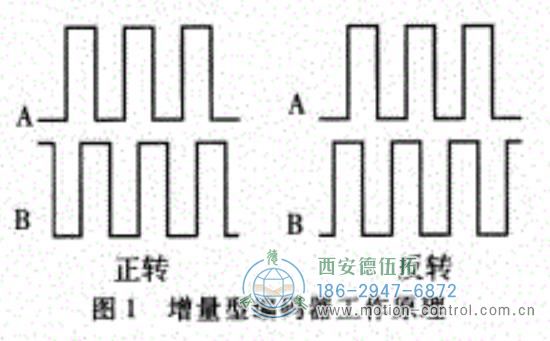

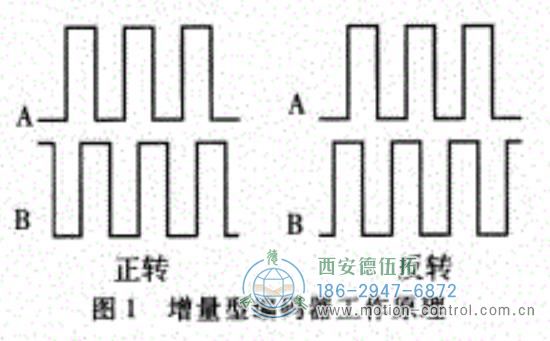

增量編碼器的工作原理

增量編碼器的工作原理是首先將位移轉(zhuǎn)換為周期性電信號,然后將該信號轉(zhuǎn)換為計數(shù)脈沖。通過這種轉(zhuǎn)換,可以測量脈沖輸出的高度的位移。如圖所示,相位A相位B顯示正向旋轉(zhuǎn),反之亦然。增量編碼器主要依靠計數(shù)來記住它們的位置,但當編碼器稍微移動時編碼器突然關(guān)閉時,當有另一個當前調(diào)用時,內(nèi)存的零點會移動,導(dǎo)致不準確和內(nèi)存丟失。我們需要添加一個參考點,即Z相位,并使用該參考位置來解決這些問題。然而,這種類型的編碼器必須首先為每個具有較差抗擾度和零點累積誤差的操作找到參考點。如果使用絕對編碼器,則可以解決這些問題。

絕對值編碼器的工作原理

絕對編碼器的碼盤包含許多光通量線,這些光通量線按2行、4行、8行、16行的順序排列。。。已訂購。這些標線片有兩個側(cè)面,即負極和正極。通過讀取每個標線片的通邊和暗邊,可以獲得一組20~2n-1的唯一二進制碼(格雷碼),這就是n位絕對值生成器。每個位置對應(yīng)一個特定的數(shù)字,這個數(shù)字是絕對唯一的,只指開始和結(jié)束,與任何中間過程都無關(guān)。在突然停電和重新啟動的情況下,參考點和零點以及脈沖數(shù)量都不需要像增量編碼器一樣重新記錄。每當你想知道這個地方在哪里,你都可以閱讀。這個編碼器的數(shù)據(jù)可靠,不容易受到外部因素的影響。

什么是SSI協(xié)議?

絕對編碼器主要將待測量的位置信息發(fā)送到主控制器,然后通過主控制器發(fā)送控制信號。以前的絕對編碼器大多使用并行輸出,這可以應(yīng)用于低位計數(shù)。一旦比特數(shù)量增加,并行輸出就不再適用,因為總是存在不準確的數(shù)據(jù)、故障等。例如,在傳輸過程中,數(shù)據(jù)電纜的任何問題都可能影響最終傳輸?shù)臄?shù)據(jù),從而影響絕對編碼器的正常操作。因此,根據(jù)實際情況,SSI協(xié)議的輸出方法更為合適。它采用串行輸出而不是并行輸出,利用差分模式提高了傳輸過程中數(shù)據(jù)的可靠性,并顯著提高了抗干擾能力。同時,通信雙方使用相同的波特率來準確地發(fā)送和接收數(shù)據(jù)。

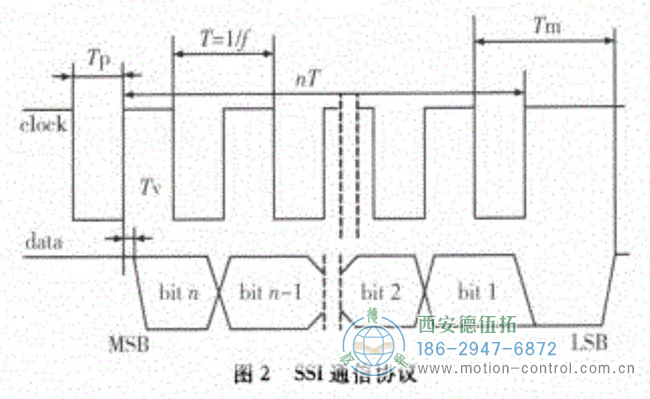

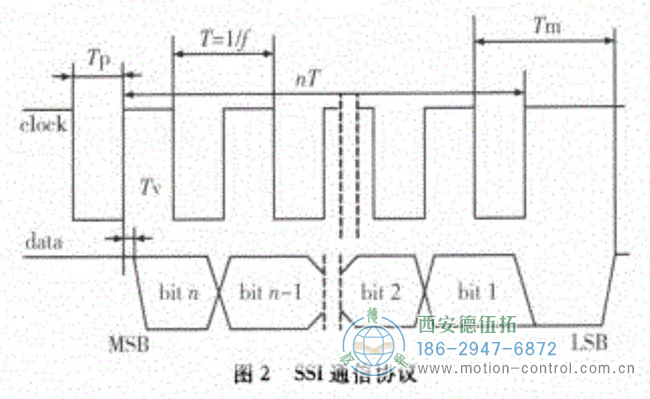

SSI協(xié)議的通信模式如圖所示。它采用主動讀接收方式,包括同步時鐘信號clock和數(shù)據(jù)信號data,其中同步時鐘的頻率決定了數(shù)據(jù)傳輸?shù)乃俣取T诠I(yè)控制應(yīng)用領(lǐng)域中,基于實際傳輸距離來選擇期望的頻率。在同步時鐘信號的控制下,從最高位(MSB)開始傳輸。在時鐘信號的第一個下降沿,要發(fā)送的數(shù)據(jù)在Tp周期期間被存儲,然后在時鐘信號每個上升沿被發(fā)送,直到所有數(shù)據(jù)被發(fā)送。然后將數(shù)據(jù)輸出端拖動到低電平,延長Tm時間,然后將數(shù)據(jù)輸入端拖動到高電平,準備等待下一個時鐘信號并繼續(xù)發(fā)送數(shù)據(jù)。如果沒有發(fā)送數(shù)據(jù),則時鐘信號和數(shù)據(jù)端子都應(yīng)保持高電平。圖2 SSI通信協(xié)議

發(fā)送數(shù)據(jù)所需的位數(shù)決定了要發(fā)送的同步時鐘的數(shù)量。圖2中的參數(shù)定義如下:T是時鐘頻率,Tp是數(shù)據(jù)之間的傳輸間隔,Tm是單穩(wěn)態(tài)觸發(fā)時間,n是傳輸位,MSB是最高有效位,LSB是最低有效位。

采用SSI接口的絕對值編碼器系統(tǒng)方案設(shè)計

主控制器可以在51芯片微控制器、RAM微處理器和CPLD邏輯器件之間進行選擇。微控制器結(jié)構(gòu)簡單,價格低廉,但運行速度慢,處理速度有限,抗干擾能力不是很強;RAM微處理器具有強大的功能,但其開發(fā)周期長,價格昂貴。為了實現(xiàn)高速傳輸,采用CPLD設(shè)計相對靈活,處理速度快,抗干擾能力強,設(shè)計時需要大量的時序和邏輯運算。

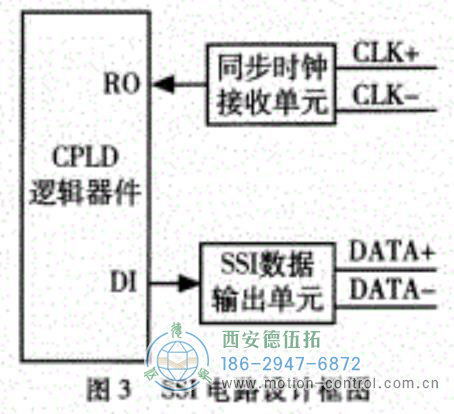

硬件設(shè)計

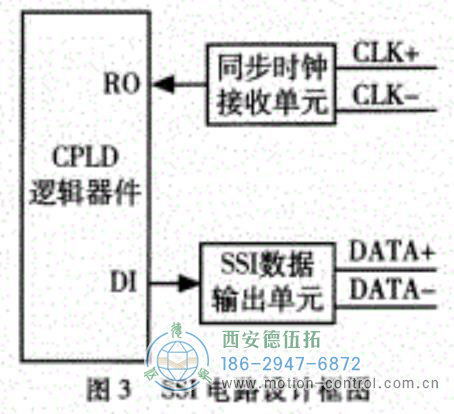

SSI電路的輸入和輸出采用差分模式,如圖所示。有四條信號線:CLK+、CLK-DATA+和DATA-,其中CLK+和CLK點是時鐘輸入,DATA+和DATA點是數(shù)據(jù)輸出。時鐘輸入端通過光耦接收,數(shù)據(jù)端通過422輸出芯片輸出。 SSI電路設(shè)計框圖

軟件設(shè)計

軟件設(shè)計

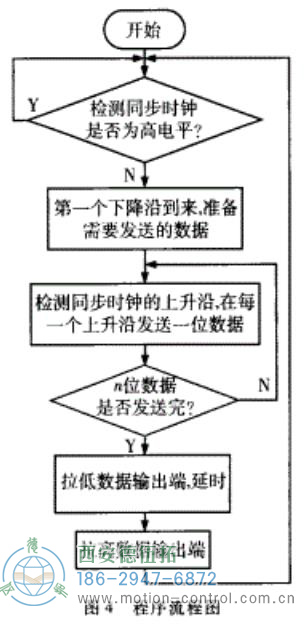

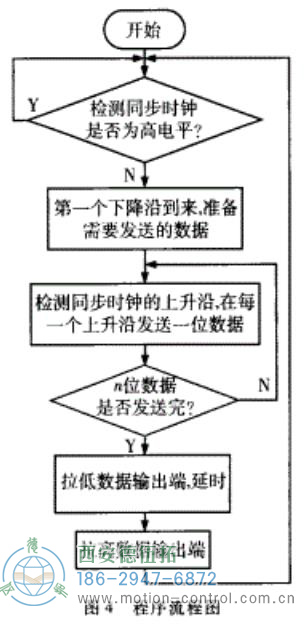

對于軟件部分的設(shè)計,SSI協(xié)議的實現(xiàn)有兩種方法:一種方法是使用微控制器模擬SSI通信,另一種方法則是使用CPLD實現(xiàn)SSI通信。微控制器仿真的關(guān)鍵技術(shù)主要包括兩個方面:同步時鐘信號的準確獲取和數(shù)據(jù)起始位的準確確定。顯然,這需要輸入和輸出端口,以及一個定時器來實現(xiàn)單穩(wěn)態(tài)觸發(fā)器。在輸入端口捕獲手表的上升脈沖,當計時器碰到手表的第一個下降脈沖時,計時器開始工作。在數(shù)據(jù)傳輸結(jié)束時,必須重置計時器才能重新開始計數(shù)。軟件流程圖如圖所示。

使用微控制器模擬SSI通信具有相對簡單的結(jié)構(gòu),但通信速度有限。為了實現(xiàn)高速通信,必須使用CPLD。

了解更多

編碼器相關(guān)知識,敬請關(guān)注西安德伍拓自動化傳動系統(tǒng)有限公司網(wǎng)站。公司技術(shù)團隊為您免費提供編碼器的選型、安裝、調(diào)試、保養(yǎng)等技術(shù)指導(dǎo)服務(wù),盡量避免企業(yè)因為編碼器技術(shù)人員的短缺帶來的損失,采取拉線上+拉線下服務(wù)的服務(wù)形式,幫助企業(yè)解決技術(shù)難題。

在線QQ

在線QQ 186-2947-6872

186-2947-6872 在線咨詢

在線咨詢

info@motion-control.com.cn

info@motion-control.com.cn